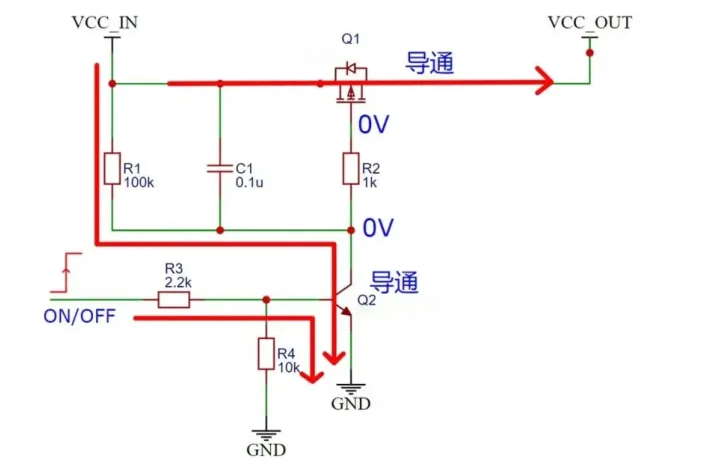

今天来分享一个超实用的电路设计 —— 基于 PMOS 的电源开关方案,通过低电压、小电流的 ON/OFF 信号,即可安全控制后级电路(VCC_OUT)的电源通断,广泛适用于嵌入式系统、电池供电设备及各类需电源管理功能的电子产品。

核心功能

实现用低压数字信号(如MCU的GPIO引脚)来控制一个更高电压、更大电流的主电源(VCC_IN)的输出。

当ON/OFF信号为低电平时,VCC_OUT无输出,电源直接切断;

当ON/OFF信号为高电平时,VCC_OUT等于VCC_IN,主电源通路导通。

当需要打开电源时:ON/OFF信号置为高电平(例如3.3V)。

电流经R3(2.2k)流入NPN三极管Q2的基极,使其饱和导通。

导通后的Q2将PMOS管Q1的栅极(G)电位拉低到接近地(GND)。

此时,PMOS管Q1的栅源极电压V_GS远小于其开启阈值电压(为负值,且绝对值很大),Q1完全导通。

电流可以从VCC_IN经Q1的源极(S)流向漏极(D),VCC_OUT端正常输出电源。

当需要关闭电源时:ON/OFF信号置为低电平(0V)。

Q2三极管因基极无电流而截止。

此时,电阻R1(100k)将VCC_IN的电压上拉至PMOS管Q1的栅极(G)。

由于Q1的栅极(G)和源极(S)电位基本相等(都约为VCC_IN),其V_GS ≈ 0V,Q1截止。

VCC_IN与VCC_OUT之间的通路被切断,VCC_OUT端无电压输出。